# The Impact of Gate Driver Loop Output Capability and Stray Parameters on Switching Performance

### Dong Jie

Infineon Technology, China

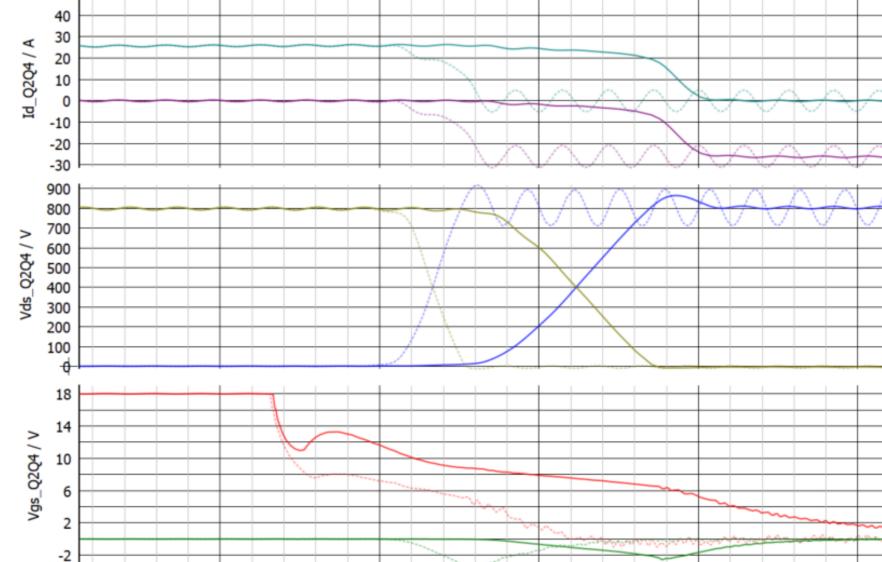

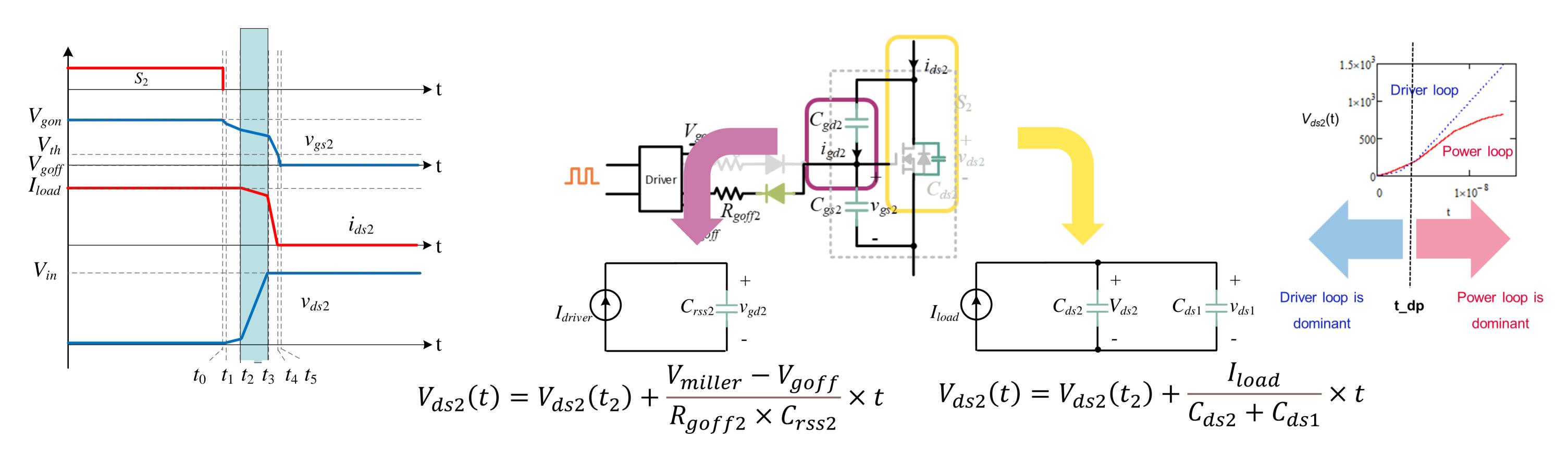

## $\succ t_2$ - $t_3$ $v_{ds}$ is limited by driver loop and power loop during turn-off

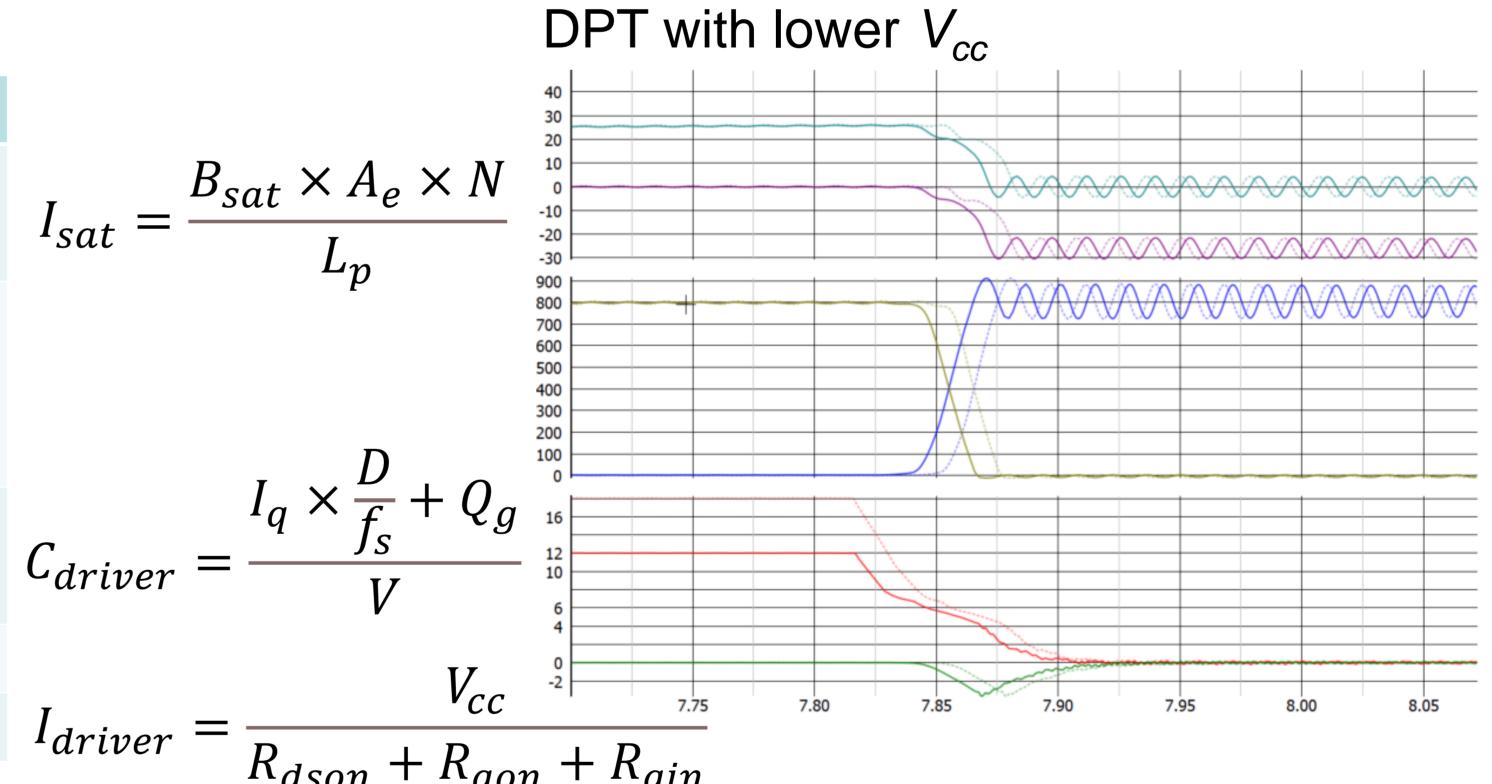

#### > Gate driver output capability

| ltem                               | Priority | Effort to adjust |

|------------------------------------|----------|------------------|

| Driver aux power: transformer      | High     | Hard             |

| Driver aux power: modulation ratio | Medium   | Hard             |

| Aux power supply capacitanc e      | Medium   | Easy             |

| Driver IC                          | High     | medium           |

| Rgon/Rgoff                         | Medium   | Easy             |

## > Gate driver stray parameters

| Item                                          | Priority | Effort to adjust |  |

|-----------------------------------------------|----------|------------------|--|

| Layout: driver loop length                    | Medium   | Hard             |  |

| Layout: driver loop laminatio<br>n            | High     | Hard             |  |

| Layout: driver loop and power loop lamination | High     | Hard             |  |

| Kelvin source                                 | High     | Hard             |  |

| Gate capacitance                              | Medium   | Easy             |  |

resistance

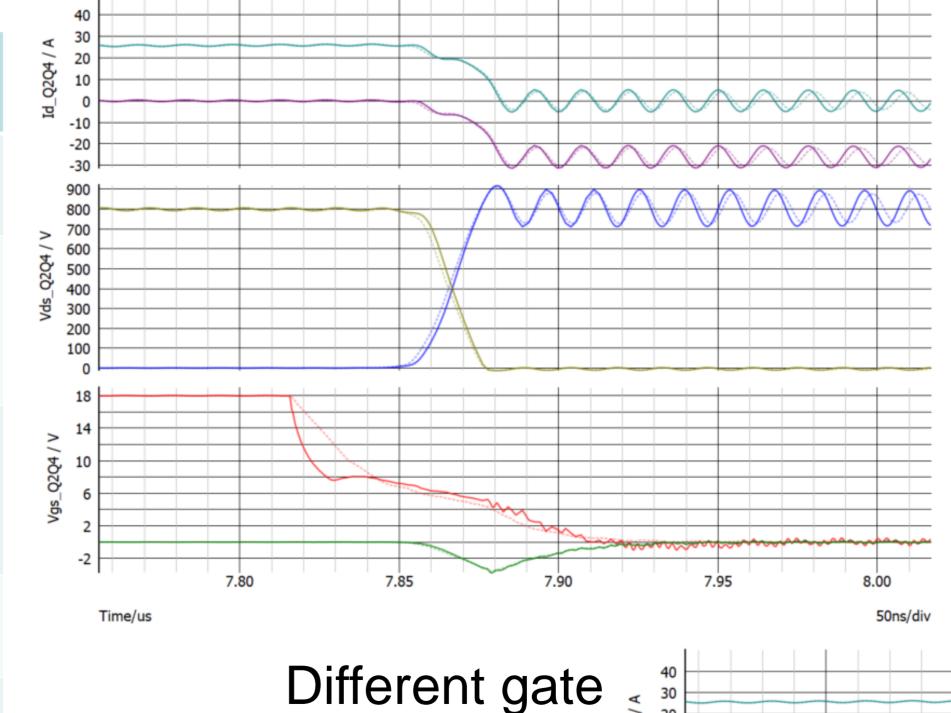

Different gate stray inductance

Driver loop length:

$$L_{driver} = 0.0002l \left[ ln \frac{2l}{W+H} + 0.2235 \frac{W+H}{l} + 0.5 \right] uH$$

Kelvin source:

$$V_{gs}(t) = V_{gon} - R_{gon} \times i_{gs}(t) - L_s \frac{di_{ds}(t)}{dt}$$