# Topic: "PowerChiplet" Technology, Ultra-high-power Density Platform for Future Power Electronics

Chair: Naoto Fuiishima, Fuii Electric, JP Organizer: Ichiro Omura, Kyushu Institute of Technology, JP

**Conference Room 1**

## Topic: "PowerChiplet" Technology, Ultra-high-power Density Platform for Future Power Electronics

Chair: Naoto Fuiishima, Fuii Electric, JP

Organizer: Ichiro Omura, Kyushu Institute of Technology, JP

#### **Motivation**

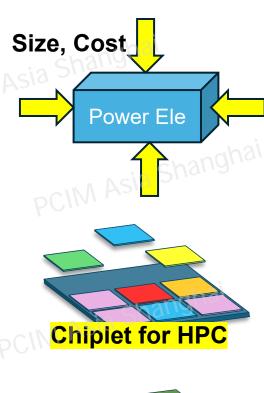

Achieving higher power density has been a key issue in power electronics, driven by the increasing demand for miniaturization in Al servers, powertrains, and on-board chargers (OBCs) for electric vehicles (EVs). However, a next-generation platform for future ultra-high-power-density power electronics has not yet been clearly defined.

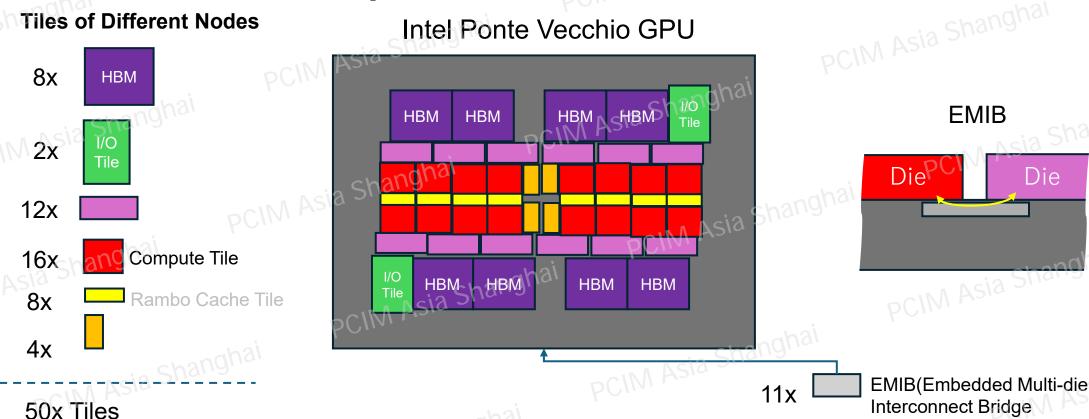

In high-performance computing (HPC), "Chiplet" technology has emerged as a future platform to address the slowdown of Moore's Law, reduce costs, and enable advanced heterogeneous integration. This concept is expected to be adopted in power electronics to achieve ultra-high-power density and a high level of system integration.

In this session, the new concept of the "PowerChiplet" will be discussed for the first time as a future platform for power electronics, with a focus on chip-embedded PCB technology. The speakers are specialists from China, Japan, and Europe. If you are interested in the future impact of "Power Chiplet" concept in power electronics as the ultra-high power density platforms, and system integration with chip embedded PCB technology, we invite you to join this session.

#### Presentations

- Power Chiplet Technology for Next Generation Power Electronics Systems

Speaker: Ichiro Omura, Kyushu Institute of Technology, JP

- Advanced Packages With Power-On-Substrate Solutions

Speaker: Frye Fung, Zhuhai ACCESS Semiconductor Co., Ltd.. CN

- Chip Embedded Panel level Power Package for Al and Vehicles

Speaker: Yoshiaki Aizawa, Aoi Electronics, JP

- Novel Integration Concepts for Power Electronics Embedding of SiC MOSFET for Highperformance Power Modules

Speaker: Lars Boettcher, Fraunhofer IZM Berlin, DE

Discussion

## Power-Chiplet Technology for Next Generation Power Electronics Systems

Ichiro Omura

Kyushu Institute of Technology

Japan

大村一郎 九州工业大学

## Agenda

- "Chiplet" for High Performance Computing

- Road Maps of Power Semiconductors

- Why "PowerChiplet"?

- Chip level

- Gate drive / Circuit level a Shanghai

- System level

- Summary

CIM Asia Shanghai

#### **pcim** asia shanghai

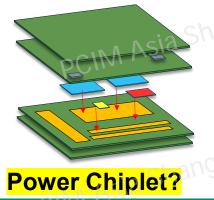

#### Chiplet, how it looks like?

Multiple Small Chips (Tiles) with Different Nodes/Functions are Heterogeneously Integrated → Cost Reduction and System Flexibility

多个具有不同节点/功能的小芯片(瓷砖)异构集成→成本降低和系统灵活性

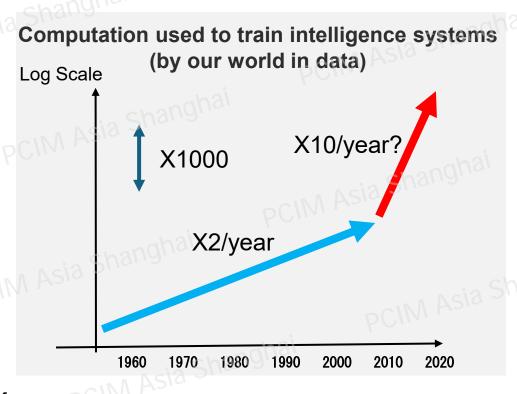

#### Al = Computation and Energy Infrastructure

https://ourworldindata.org/grapher/artificial-intelligence-training-computation

https://www.ark-invest.com/articles/analyst-research/ai-

training?ref=blog.paperspace.com

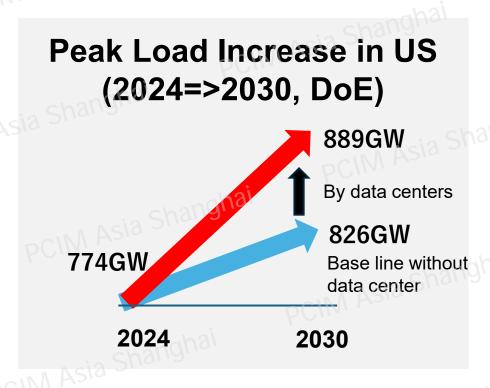

#### Growth rate of 10GW/Year (only for data center)

Data from DoE, Resource Adequacy Report Evaluating the Reliability and Security of the United States Electric Grid July 2025

Energy may limit Al Development Speed 能源供应可能限制人工智能的发展速度。

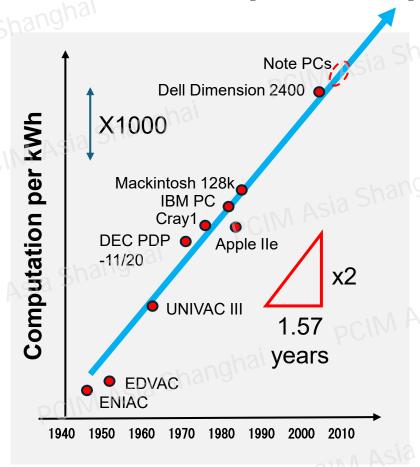

#### **Computation per Energy and Transistor Size**

Data from: J. Koomey et al., "Implications of Historical Trends in the Electrical Efficiency of Computing," in *IEEE Annals of the History of Computing*, vol. 33, no. 3, pp. 46-54, March 2011

Data from https://www.tel.co.jp/museum/magazine/report/202310\_01/

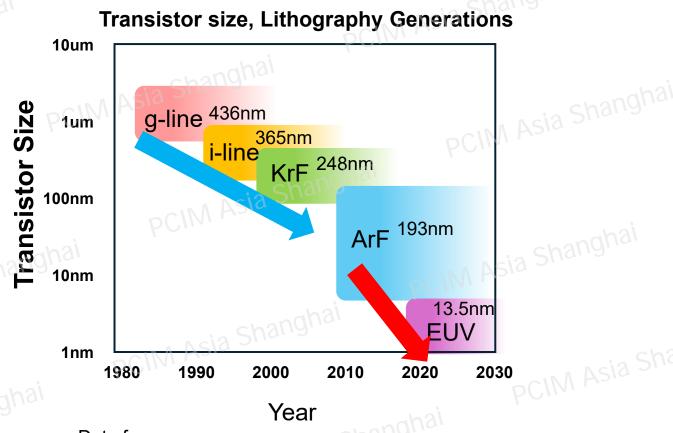

#### Minimizing of Transistor Size is the Solution

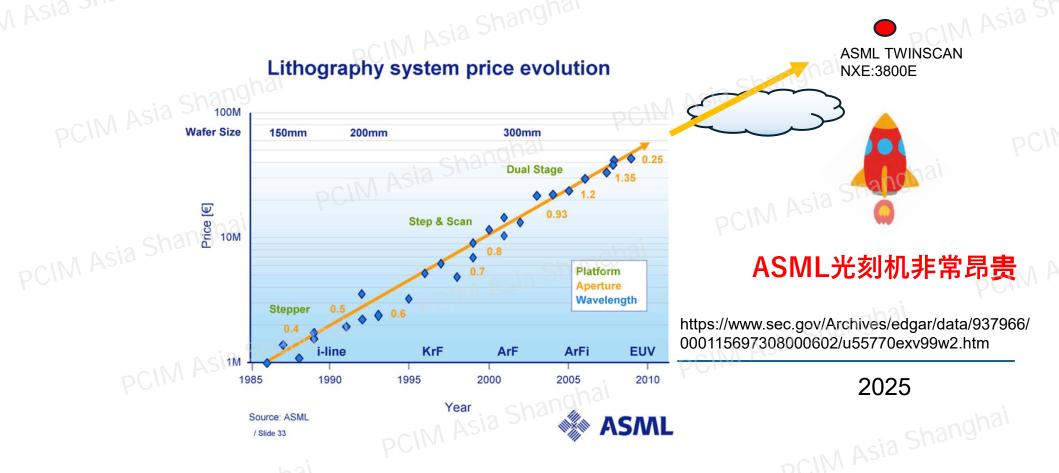

#### **ASML Lithography System Price**

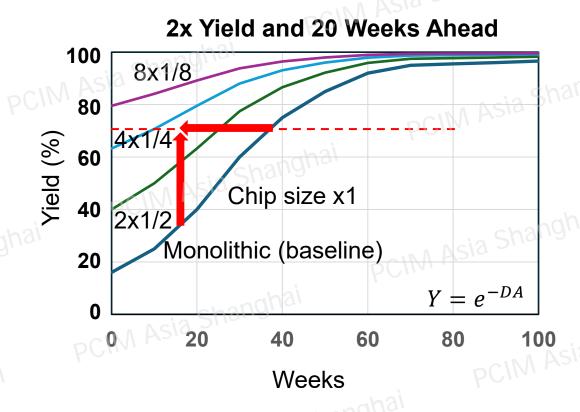

**Increasing Chip Costs and Decreasing Yield**

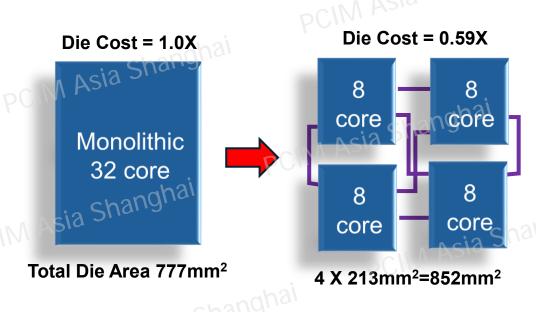

#### "Chiplet", Smaller Chip Concept

Deta from: L. T. Su et al., "Multi-chip technologies to unleash computing performance gains over the next decade, IEDM 2017, doi: 10.1109/IEDM.2017.8268306.

#### Chiplet Technology Reduces the Cost and Shorten the Development Cycle

"芯粒"技术可降低成本并缩短开发周期

#### **Chiplet Technology Overview**

- 1. A chiplet is a technology that integrates **small chips** into a package to build **large-scale systems**.

- 2. It enables heterogeneous integration of circuits and functions across different process nodes, while offering high design flexibility in system architecture.

- 3. Applying chiplet technology may allow the growth of computation per kWh for future AI technology with lower cost.

## Agenda

- "Chiplet" for High Performance Computing

- Road Maps of Power Semiconductors

- Why "PowerChiplet"?

- Chip level

- Gate drive / Circuit level a Shanghai

- System level

- Summary

CIM Asia Shanghai

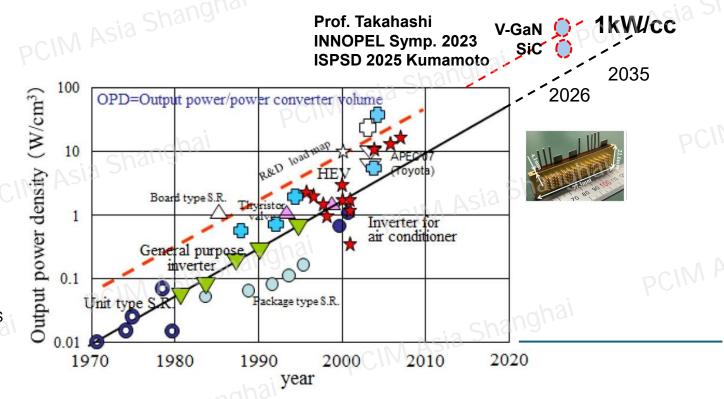

#### **Power Electronics Power Density Trend toward 2035**

H. Ohashi, I. Omura, Role of Simulation Technology for the Progress in Power Devices and Their Applications, IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL.60, NO.2, 2013

#### Power Density Increase 10x for Every 15 Years → 1kW/cc in 2035

预计功率密度每15年增长10倍,到2035年将达到1 kW/cm³。

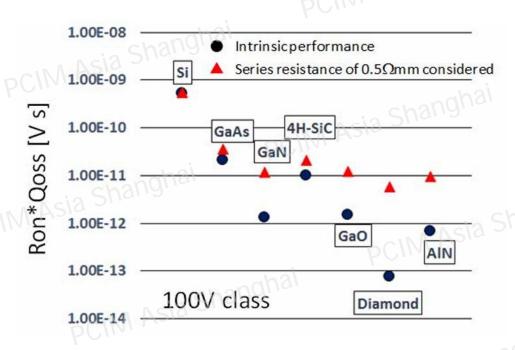

T. P. Chow, I. Omura, M. Higashiwaki, H. Kawarada and V. Pala, "Smart Power Devices and ICs Using

Semiconductors," in IEEE Transactions on Electron Devices, vol. 64, no. 3, pp. 856-873, March 2017

GaAs and Wide and Extreme Bandgap

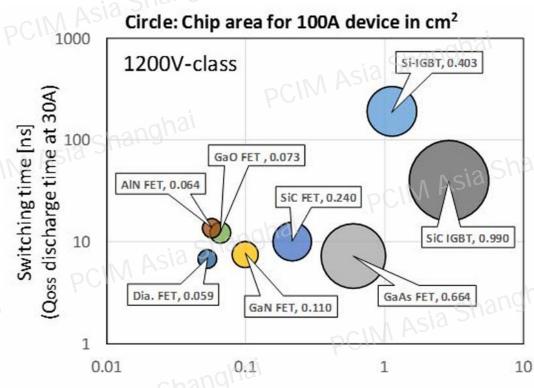

### **WBG Power Semiconductors** PCIM Asia Shanghai

**Vertical Device**

Forward voltage drop [V] at 30A

Higher Switching Speed and Lower Conduction Loss with Smaller Chip Size 但开关速度更快,导通损耗更低,芯片尺寸更小。

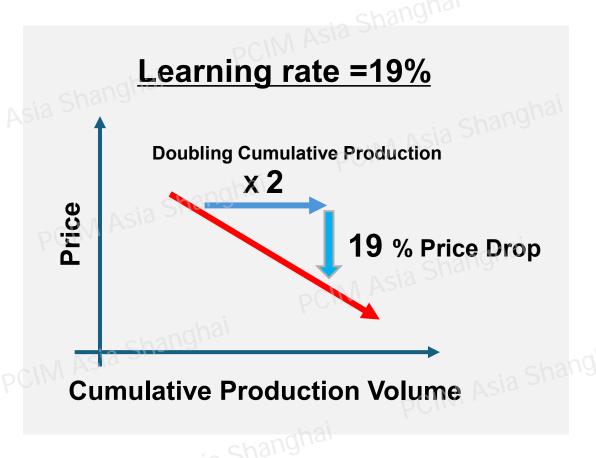

#### **Power Electronics Price Trends**

|                 | PCIM Asia Shanghai  |                                                                                     |  |

|-----------------|---------------------|-------------------------------------------------------------------------------------|--|

| ltem            | Learning Rate       | Source                                                                              |  |

| PV module       | 20%                 | 5 - F - D(                                                                          |  |

| Onshore wind    | 19%                 | Bloomberg New Energy Finance                                                        |  |

| Li-ion Battery  | 19%\sia             | Hannah Ritchie, Our world in data,<br>2021                                          |  |

| PV inverter     | 7% <del>→</del> 19% | Agora report, Fraunhofer ISE,<br>Current and Future Cost of<br>Photovoltaics, 2015, |  |

| DRAM/Flash      | 35%                 | Walden Rhines, Predicting                                                           |  |

| Remaining Semis | 23% PC              | Semiconductor Business Trends<br>After Moore's Law, 2019                            |  |

Ichiro Omura,

Power Electronics for a Future Sustainable Society,

Keynote at PCIM2022 Nurnberg, May 11, 2022

#### Rapid Price Reduction for Production Volume Increase

生产量增加导致价格迅速下降

Ichiro Omura.

Paper 14.2

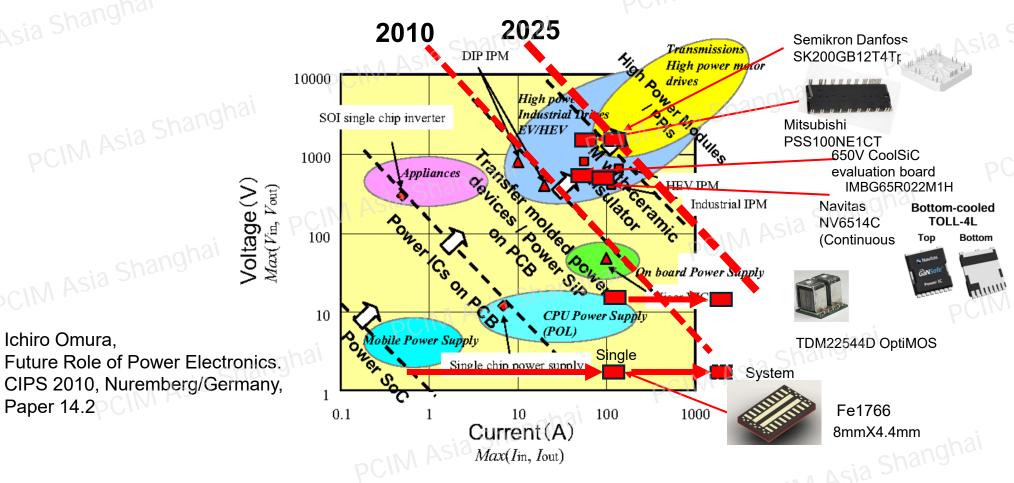

#### Power on/in PCB

#### 10x for 15 years

PCB Technology is the Key to Reduce the Costs and Size

## Agenda

- "Chiplet" for High Performance Computing

- Road Maps of Power Semiconductors

- Why "PowerChiplet"?

- Chip level

- Gate drive / Circuit level a Shanghai

- System level

- Summary

CIM Asia Shanghai

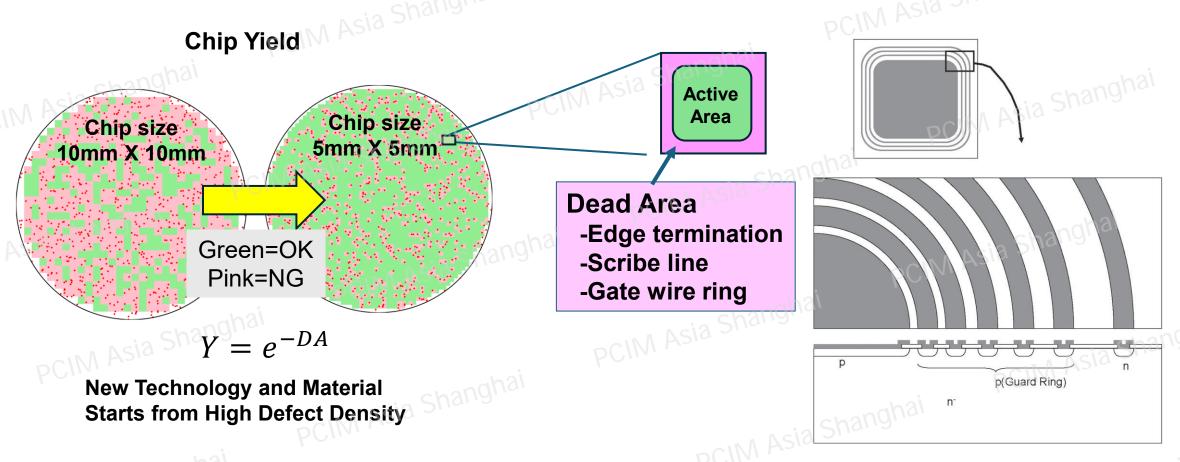

#### "Active Area" Yield

#### **Area Ratio of Total Produced Active Area**

#### "Active Area" Yield for Dead Area on Chip

For WBG (High Ecrit), Small Chip Size are Optimum

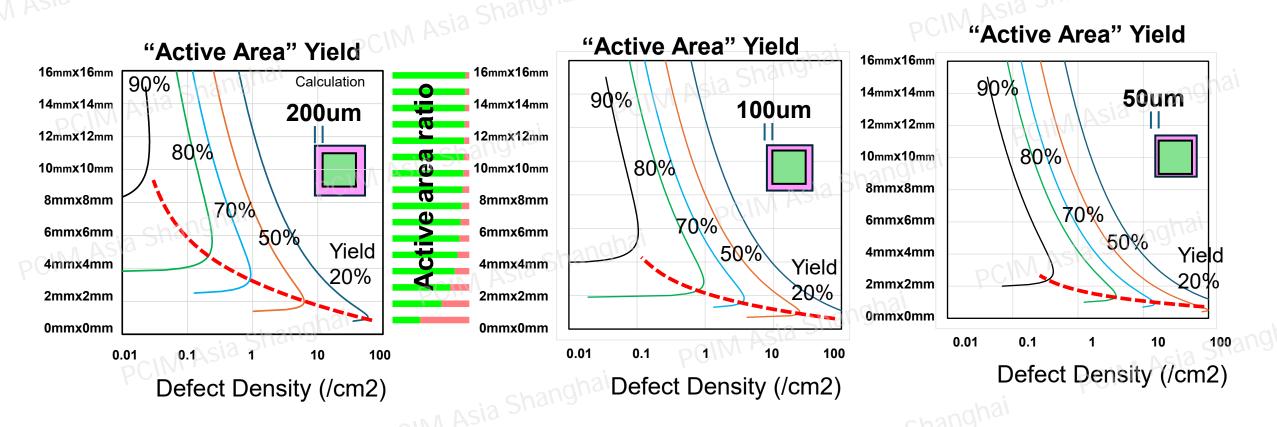

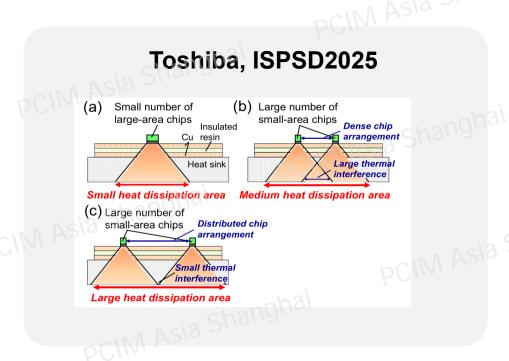

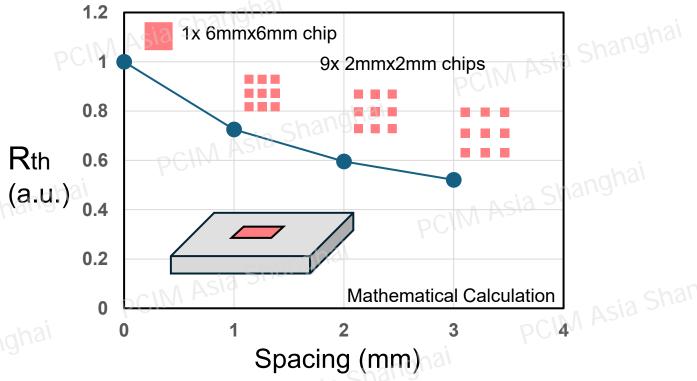

#### Multiple Small Chip Layout for Better Cooling

#### Thermal Resistance for Spacing

#### Small Chip Layout Reduce Rth by Half

分布式小型芯片布局将Rth减半

M Asia Shanghai

## Agenda

- "Chiplet" for High Performance Computing

- Road Maps of Power Semiconductors

- Why "PowerChiplet"?

- Chip level advantage

- Gate drive / Circuit level Shanghai

- System level advantage

- Summary

CIM Asia Shanghai

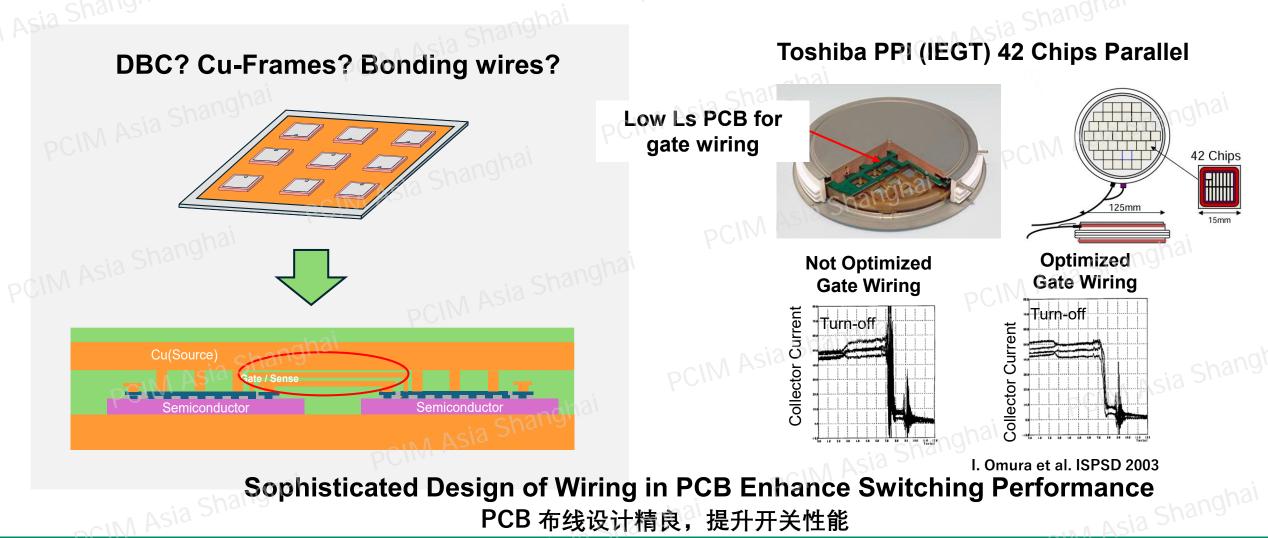

#### Low Inductance Wiring for Stable Switching

#### Issue of Parasitic Inductance for High-Speed Switching

#### **Ultra High-Speed Lateral Devices**

| T. P. Chow et al., in IEEE Transactions on Electron | on Devices, vol. 64, no. 3, pp. 856-873, |

|-----------------------------------------------------|------------------------------------------|

| March 2017                                          |                                          |

|  | <b>GaN Transistor</b> | Supplier | di/dt  | VDC  | Remarks                 |  |

|--|-----------------------|----------|--------|------|-------------------------|--|

|  | GS66516T              | GaN Sys. | 18A/ns | 400V | S. Satpahy, Simul. 2021 |  |

|  | EPC1010               | EPC      | 9A/ns  | 100V | M, Danilovic, 2018      |  |

|  | EPC2015C              | EPC      | 15A/ns | 20V  | K. Wang, 2011           |  |

K. Wang et al., IEEE Trans. on PE, 2018, doi: 10.1109/TPEL.2017.2749249.

M. Danilovic et al, ECCE 2011, doi: 10.1109/ECCE.2011.6064128.

S. Satpathy et al., ECCE-Asia), 2021, doi: 10.1109/ECCE-Asia49820.2021.9479426.

Very Low Ls (Self or Mutual) Wiring is Required for Advanced Devices 高级设备需要极低的 Ls(自感或互感)接线

## Agenda

- "Chiplet" for High Performance Computing

- Road Maps of Power Semiconductors

- Why "PowerChiplet"?

- Chip level

- Gate drive / Circuit level a Shanghai

- System level

- Summary

CIM Asia Shanghai

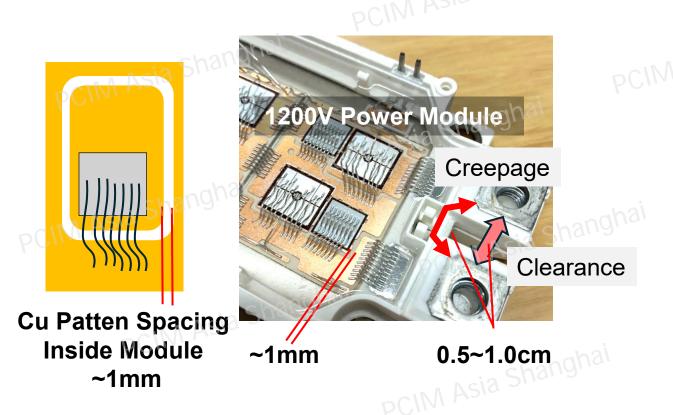

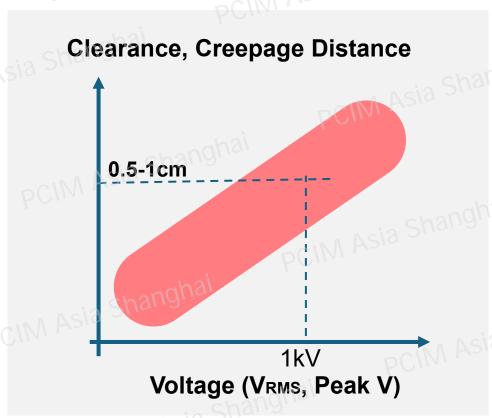

## Interconnection between Chips and Power Circuit Clearance and Creepage Distance

Wiring and Connection INSIDE the PCB to Reduce the Size

### **Needs of System Integration** PCIM Asia Shanghai

#### **Complexity of Device Operation**

**Lateral Bidirectional Device Case**

Peripheral Circuits of Chip Need to be Integrated to be the System

芯片外围电路需集成成系统

System

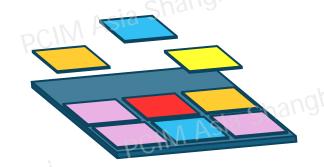

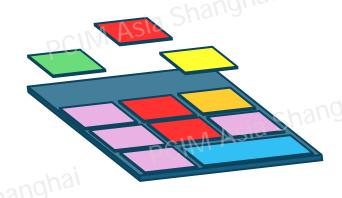

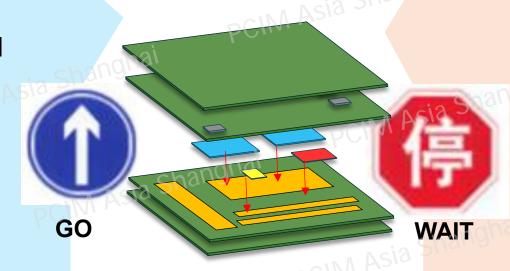

#### **Chip Embedded PCB**

#### Packaging - System

Level 1: New Packaging of Existing Products

Packaging

Utilizing existing semiconductor products with updated packaging

technologies.

Level 2: PowerChiplets Using Existing Chips Sub-system

Combining existing power chips and gate drivers etc. as "Tiles" to enhance modularity and integration.

Level 3: PowerChiplets with Dedicated Chips Sub-system Plus

Developing power chips and gate driver etc. specifically designed for PowerChiplet.

**Level 4: System-Level Power Chiplets**

Constructing entire power electronics systems using PowerChiplet technology.

Chip - PCB

Chip / PCB

**Individual Design**

Co-Design

## Agenda

- "Chiplet" for High Performance Computing

- Road Maps of Power Semiconductors

- Why "PowerChiplet"?

- Chip level advantage

- Gate drive level advantage

- System level advantage

- Summary

CIM Asia Shanghai

#### Why PowerChiplet

- Chip Level

- Chip Cost Reduction

- Thermal Resistance Reduction

- Gate Drive / Circuit Level

- Stable Switching (No oscillation)

- High Speed Switching (Reduction of Ls)

- > Solve the Complexity

- System Level

- Size Reduction of Connection to Power Circuit (Creepage, Clearance)

- PE System Level Cost Down

**PowerChiplet**

- > Test

- Co-Design

- ➤ Standard (3DBlox?)

- > Reliability

- > Cost

- > Recyclability

- Passive Components

- ➤ Isolation (Electrical, Thermal, Signal)

- > Others

#### Presentations

- Power Chiplet Technology for Next Generation Power Electronics Systems

Speaker: Ichiro Omura, Kyushu Institute of Technology, JP

- Advanced Packages With Power-On-Substrate Solutions

Speaker: Frye Fung, Zhuhai ACCESS Semiconductor Co., Ltd.. CN

- Chip Embedded Panel level Power Package for Al and Vehicles

Speaker: Yoshiaki Aizawa, Aoi Electronics, JP

- Novel Integration Concepts for Power Electronics Embedding of SiC MOSFET for Highperformance Power Modules

Speaker: Lars Boettcher, Fraunhofer IZM Berlin, DE

Discussion

#### Packaging for PowerChiplet

#### **Power Module**

Chip

Solder on DBC

↓

Solder on Base Plate

↓

Housing + Silicone

filler + Lead frame

↓

PCB for gate wiring,

Controlling

↓

Assembling to heat sink

Wire Frame connection

#### **Transfer Mold Module**

Chip

↓

Solder on Lead Frame

↓

Molding

↓

Assembling to PCB

↓

Heat sink

#### **Chip Embedded PCB**

Chip

↓

Assembling in PCB Process

with other chips

↓

Heat sink

Schweizer

Infineon