# Chip Embedded Panel level Power Package for Al and Vehicles

Yoshiaki Aizawa, Katsuhiro Takao AOI ELECTRONICS CO.,LTD.

#### **FOLP® Technology Direction (Trend)**

RDL-first (fine pitch/multi-layer)

**High Frequency**

Multi-Layer, 3 D FOLP®

Chiplet Chiplet

High Via connection reliability

Deep plugged Via

Low RF signal loss

(Low Df material)

Fine pillar pitch

Fine Line/Space

High yield (Simple structure)

**High-end Logic**

Fine pitch FOLP® Chiplet

Chip-first (high heat dissipation/low resistance)

Thinner, Heat dissipation FOLP®

Low electrical resistance wiring

Low inductance wiring

High heat dissipation

(High thermal conductive material)

High operation temperature

(High Tg material)

#### **Outline**

- √ Background

- Why are Chip Embedded Packages required?

- Chip Embedded Package Technologies

- √ Chip Embedded Power Package for Al/Date center applications

- Coreless Chip Embedded Technology (AOI Panel Level Package) Ex. Thin Multi chip voltage regulator (and with built-in inductor)

- ✓ Chip Embedded Power Package for Automotive applications- Power Sub Module

- Packaging Technologies

- AOI Panel Level Power Chip Embedded Technology

Ex. Chip embedding process with thick Cu RDL

Cu direct plating on the back side of power chips

- ✓ Summary

PCIM Asia Shanghai

#### **Background**

pcim ASIA SHANGHAI

- ◆ Power semiconductor plays as a key role in the rapid development of automotive (EV) due to environmental issues

- ◆ Al/data center require high efficiency power supply system due to increasing power consumption

- ◆ As power supply output current increasing, wiring resistance is a big issue about power distribution loss.

- Reducing parasitic inductance, wiring resistance, and shortening the current loop are necessary in high density environment.

- Chip-embedded packages (PoP/CoP/3D-SiP) can shrink size and increase current density.

- ◆ Inverters and DC/DC converters are the need for efficient power management system.

Source : NTT Corporation

Source : TOYOTA corporation

## Why are Chip Embedded Packages required? PCIM Asia Shanghai

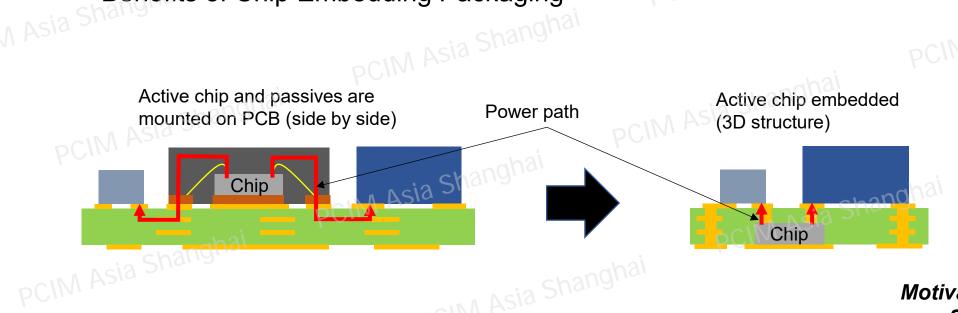

Benefits of Chip Embedding Packaging

Motivation Smaller and Thinner package Lower resistance PCIM Asia Shangl Lower inductance

Source : NEPCON Japan 2025 Fraunhofer IZM

#### **Chip Embedded Package Technologies ASIA SHANGHAI** Power core Module Package **SESUB** Source: IMAPS Advanced Packaging for Power Electronics 2024 AOI Source: ASE Thinner Power Module Package PCB Substrate base **MCeP** Cu Core Solder Ball Panel base (Panel level package) Electrode PAD EMC Sintering Ag paste Source: IMAPS DPC 2023 AO Lead frame base Source: SHINKO Corporation **MDQFN** P2 Pack PCIM Asia aEASIP1 Source: DECA Lead PCIM Asia Shanghai PCIM Asia Shang. Lead frame Source : ASE **GaNFET** Source: Schweizer Corporation

# Chip Embedded Power Package for Al/Data center applications

Political and a series of the series of the

Source : NTT Corporation

7

#### AI / Data center Application

#### Applications : Power Supply System

Source: NTT Corporation

# Data center energy consumption per year Sensitivity analysis (10,000 replications) - All scenarios 1400 1200 1200 1200 99% Confidence interval 95% confidence interval 75% confidence interval 55mulation results - Median Masanet et al. (2020) - incl. traffic Andrae et al. (2020) - best

Source: University of Twente, the Netherlands

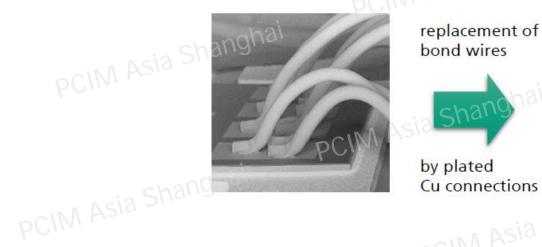

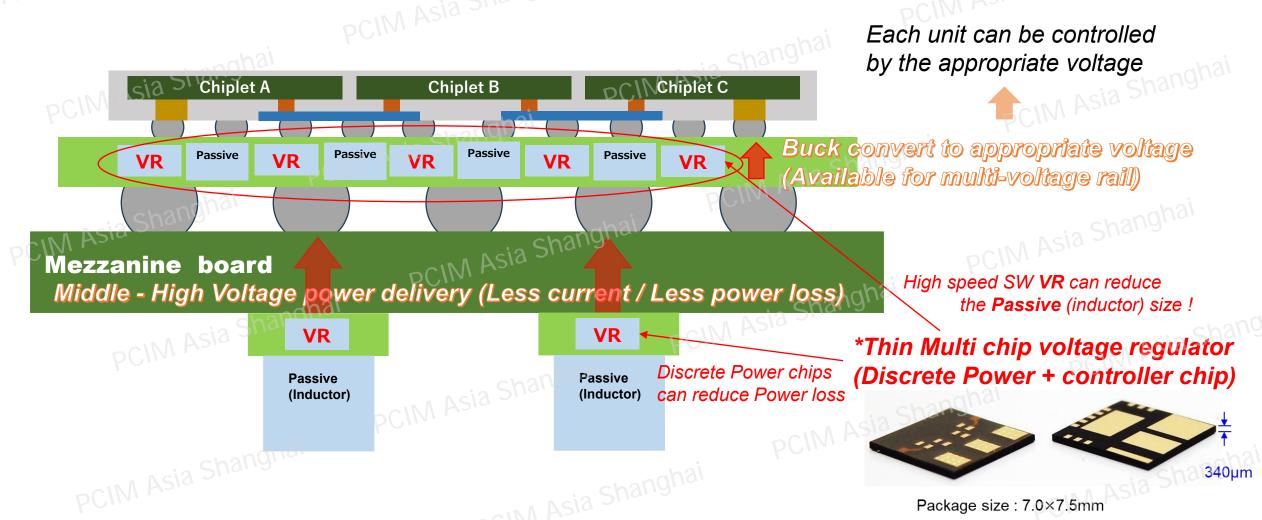

- ✓ Al/Data Center requires high efficiency power supply system at both high voltage and low voltage levels due to increasing power consumption.

- ✓ As power supply output current and switching frequency increase, wiring resistance and inductance are a major concern for power distribution losses and power integrity.

- ✓ Regarding the low voltage stage, placing the voltage regulator (VR) and passives close to the active die (CPU/GPU/HBM, etc.) is very important for power integrity (PI).

- Substrate embedded VR and passives are a good solution for PI improvement.

- ✓ The embedding of the power module and inductor is a big challenge due to the high profiles.

#### Power delivery structure of the AI server system

#### Today's typical system

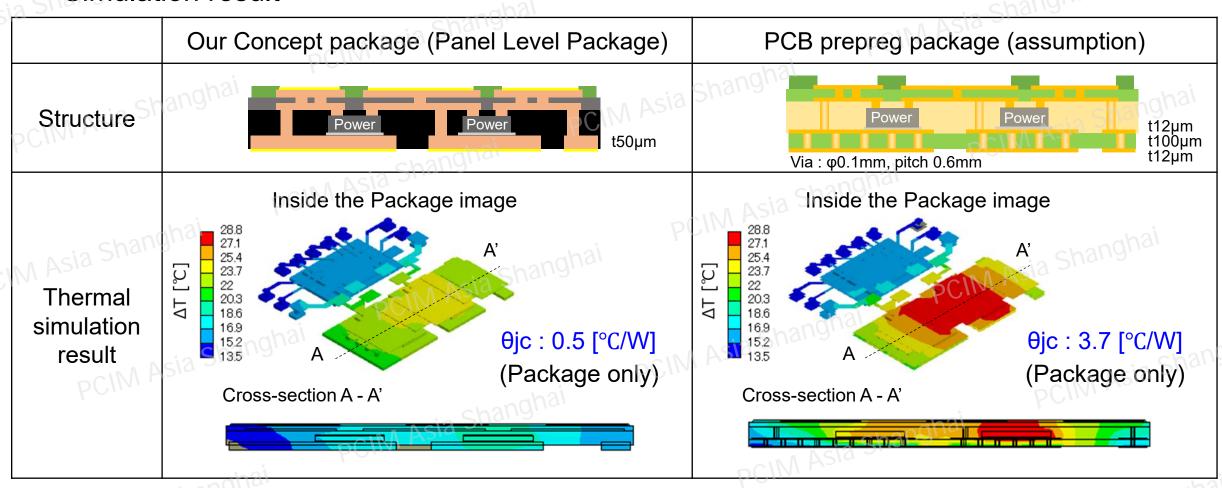

# Thermal Resistance Simulation Comparison between Panel Level and PCB Based Package

#### ■ Simulation result

The thermal resistance of our concept package is very low, and it has the advantage of quickly dissipating heat to the substrate side.

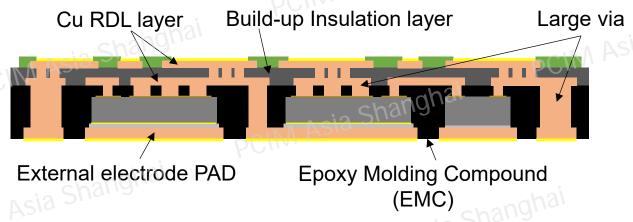

#### Coreless Chip Embedded Technology (AOI Panel Level Package)

AOI's new approach of *Ultra thinner*, *Higher heat dissipation* chip embedded technology in analog and power solutions.

#### Features of this concept

- Unique Coreless structure with all-Cu plating embedding method, using power customized fan-out processes

- Panel form of 300 mm square with cost benefit

- Smaller and Ultra thinner module package with coreless structure

- Excellent thermal property with large electrode pad and large via filling

- High reliability and short TAT with one stop solution (from panel substrates to package assembly in-house)

Source: IMAPS DPC 2023 AOI

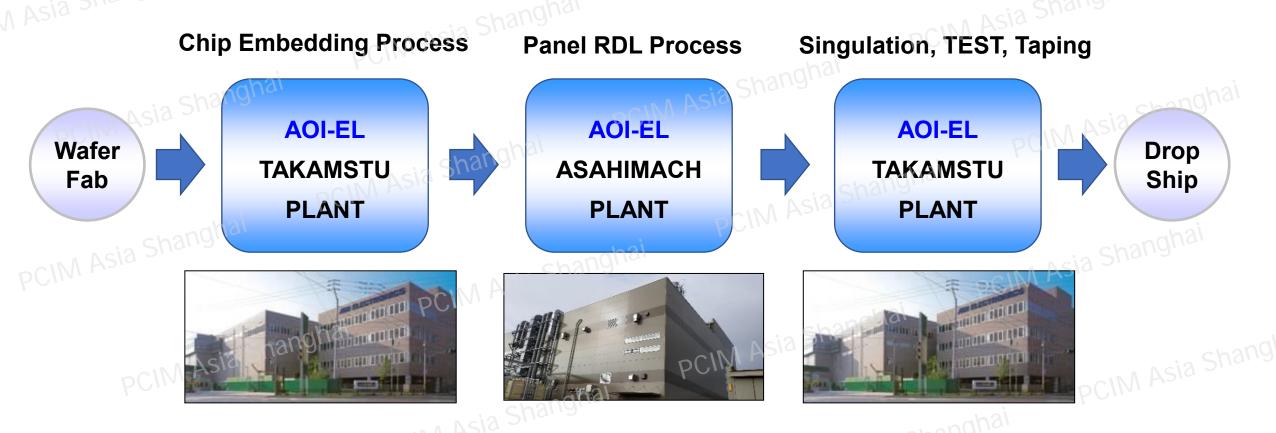

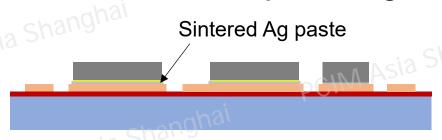

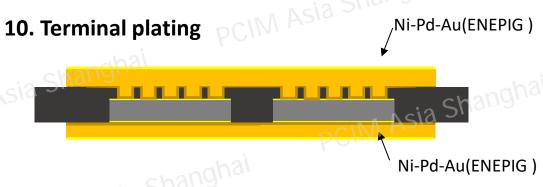

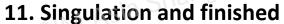

#### **Manufacturing Process Flow for a Prototype**

Panel level package manufacturing flow

We can perform one-stop production in-house, from panel substrates to chip embedding process, panel RDL process and package assembly.

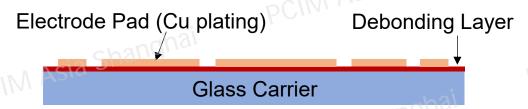

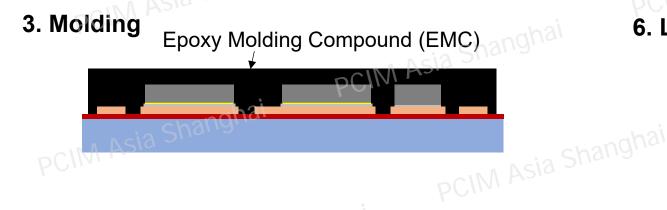

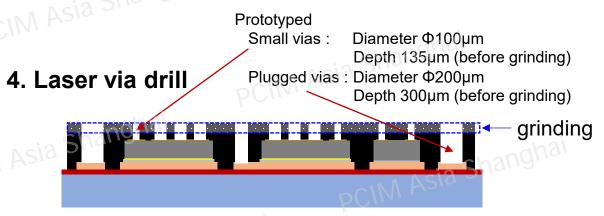

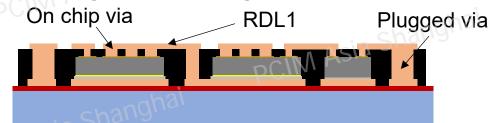

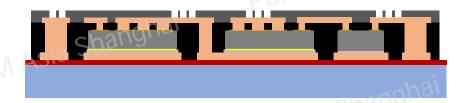

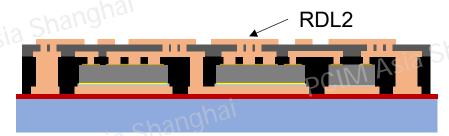

#### **Basic Process Flow for a Prototype**

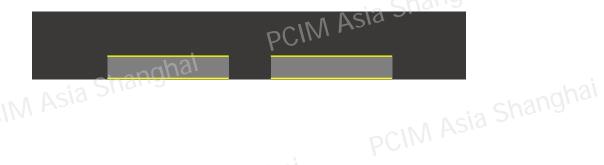

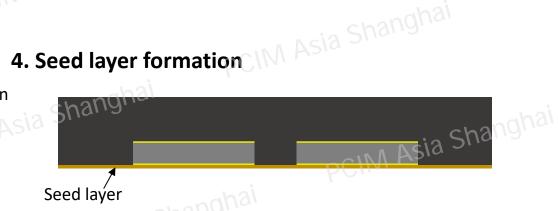

- Basic Process flow (1)

- 1. Electrode Pads Formation on Glass Carrier

2. Controller and Power Chips Bonding

5. Cu plating for Via-filling and RDL1

6. Laminating for Insulation layer Insulation layer

# **Basic Process Flow for a Prototype** PCIM Asia Shangha

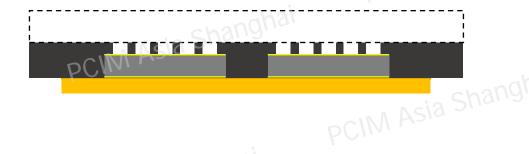

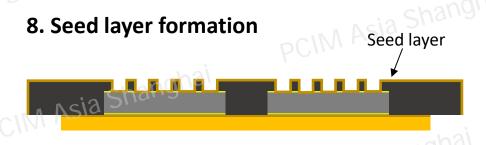

- Process flow (2)

- 7. Laser via drill

8. Cu plating for Via-filling and RDL2

9. Solder resist formation

#### 10. Glass Carrier Debonding / Terminal plating / Singulation

#### Our usual inspection or test

- Pattern inspection for each process

- Open/short test for checking internal connection

- Optional function test

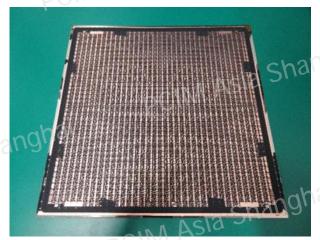

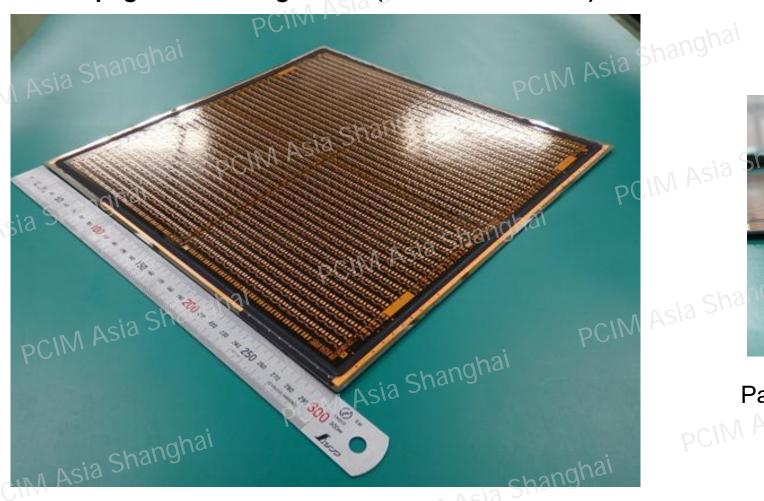

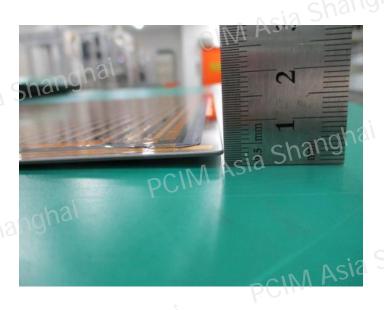

## Trial production and evaluations for a Prototype PCIM Asia Shang

300 mm square Panel-level photo

**Warpage Before singulation (with Glass Carrier)**

Panel warpage: 2mm Maximum

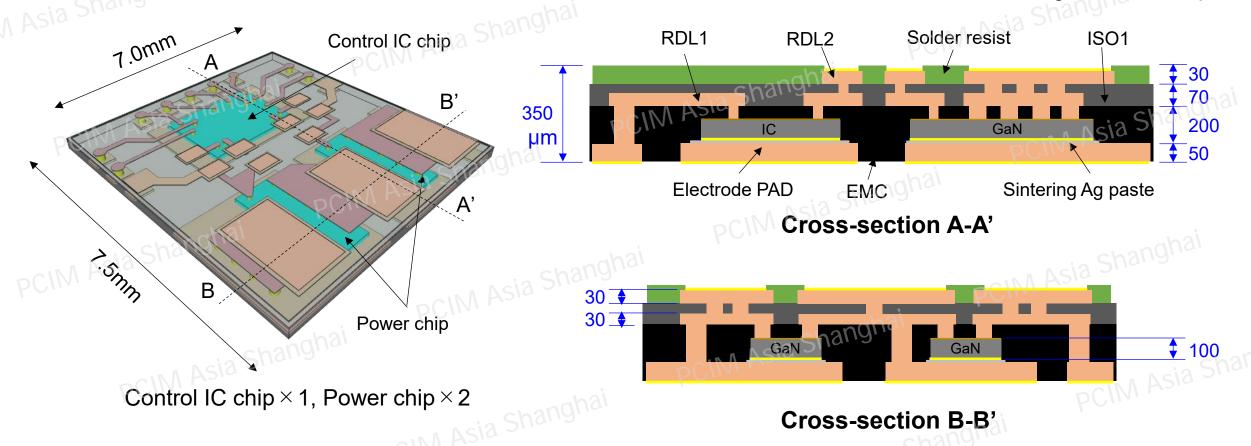

#### Package structure

Prototype package structure

Design value /unit : µm

- · Ultra-thin & high heat dissipation module with DC-DC half-bridge structure. PCIM Asia Shang

- Motif of GaN HEMT for power and high-speed switching.

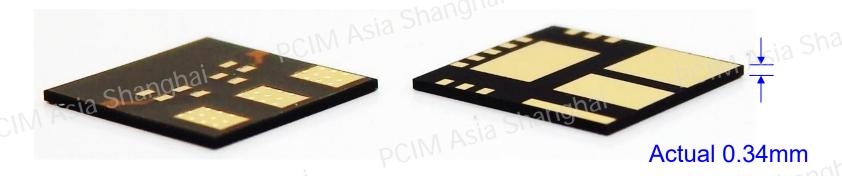

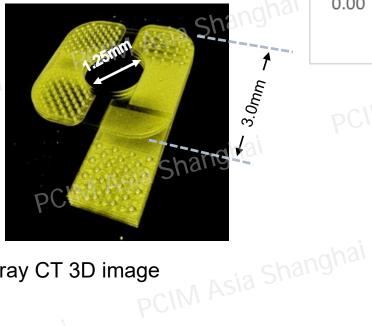

#### Package thickness & X-ray CT 3D image

Prototyped package

Package thickness

#### New Coreless chip embedded module package

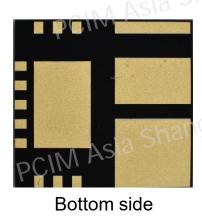

Top side

Bottom side

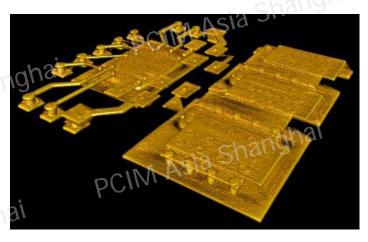

X-ray CT 3D image (Internal structure)

Package size: 7.0×7.5mm

Our proposed new Coreless chip embedded package thickness is actual 0.34mm. It is very thin compared to conventional power QFN.

Very thin SoC-like analog and power module package such as heterogeneous chip bonding can also be realized.

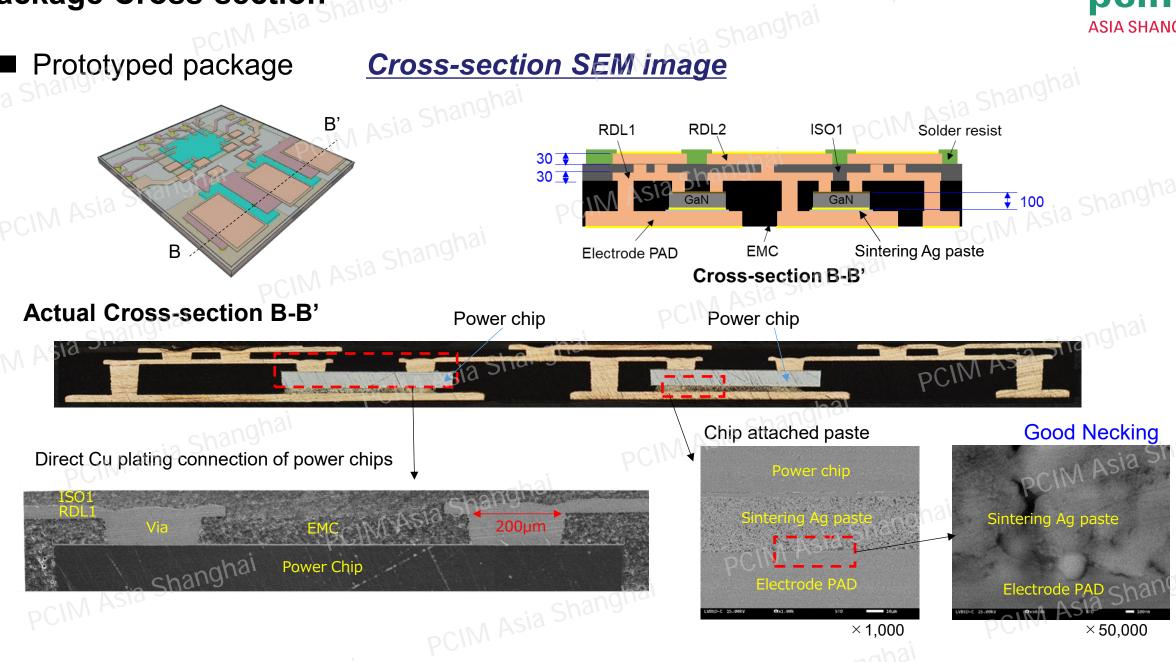

#### **Package Cross-section**

Prototyped package

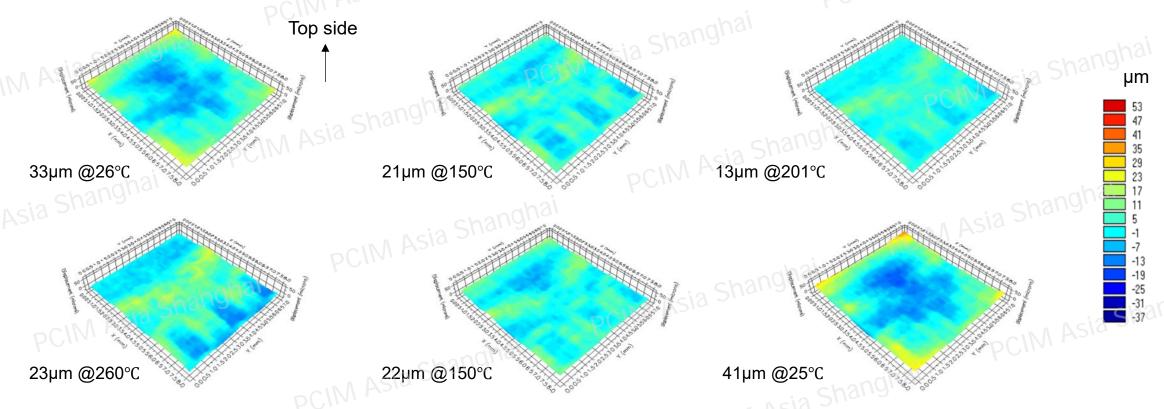

#### Warpage (coplanarity) evaluation result of package level

Package warpage

#### Warpage Behavior in the Reflow Temperature Range using shadow moiré method (3D Plot)

At room temperature, warpage was maximized (less than 50µm) with smile shape. At high reflow temperature, warpage became small, tended to be flat.

#### Thin Multi chip power module for Chiplet integration device application

Suitable power delivery by IVR (Integrated Voltage Regulator)

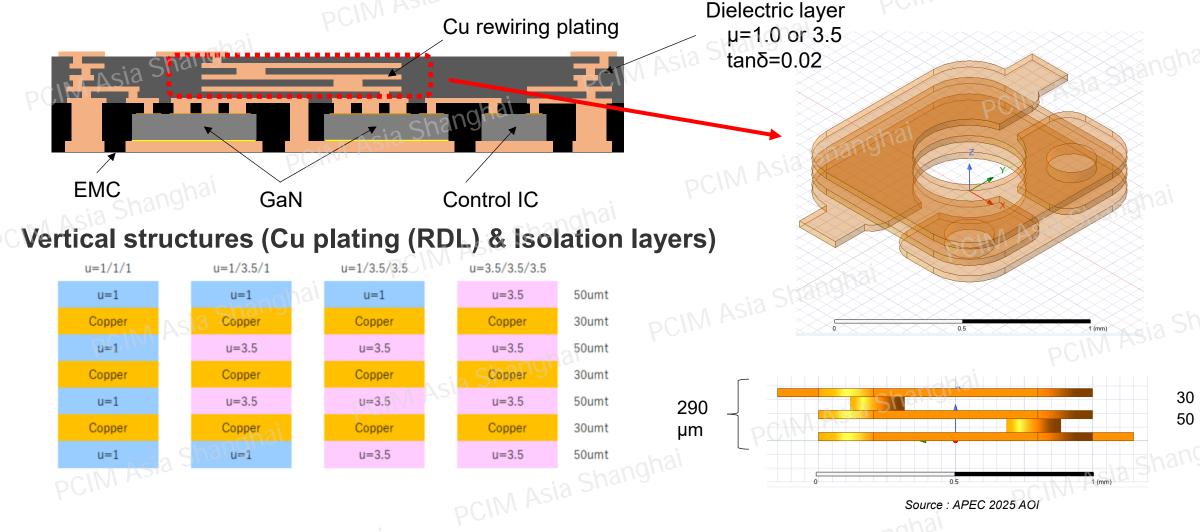

#### Thin GaN HEMT voltage regulator with built-in inductor

■ GaN HEMT voltage regulator with a built-in inductor formed by Cu rewiring plating (RDL)

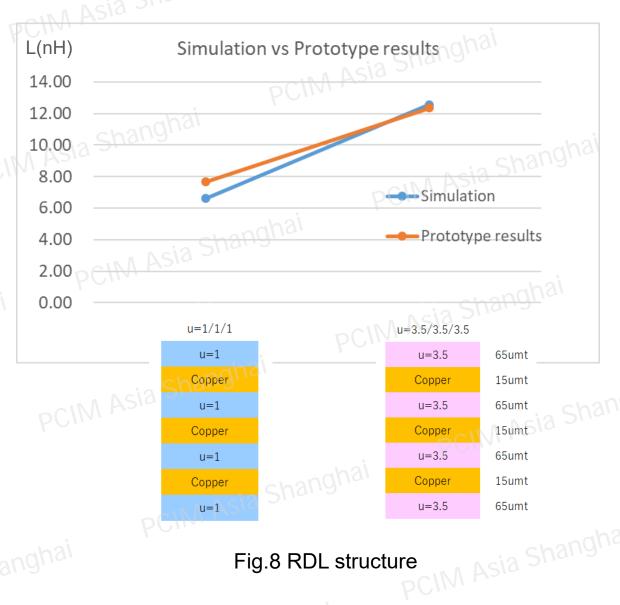

#### Simulation vs Prototype measurement results

#### Inductance Simulation vs Prototype results

#### Structual conditions

► Inductor size : 3.0mm

► Inner hole diameter : 1.25mm

Frequency: 100MHz

► Vertical structures (RDL & Isolation)

$\Rightarrow$  Fig.8

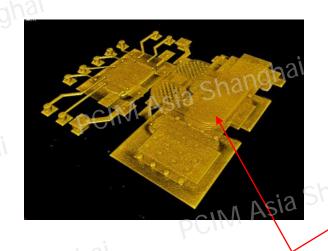

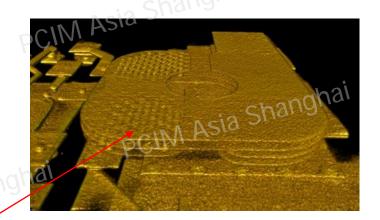

Prototype Photo & X-ray CT 3D image

Fig.8 RDL structure

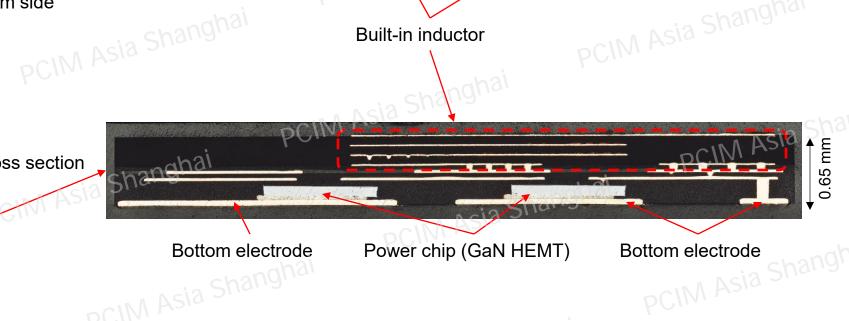

#### Thin GaN HEMT voltage regulator with built-in inductor (PoC)

#### Prototype package outline

X-ray CT 3D image

PCIM

Cross section

**Built-in inductor**

# Chip Embedded Power Package for Automotive applications

PCIM Asia Shanghai

PCIM Asia Shanghai

PCIM Asia Shanghai

PCIM Asia Shanghai

Source : TOYOTA corporation

24

#### SiC inverter module

#### pcim ASIA SHANGHAI

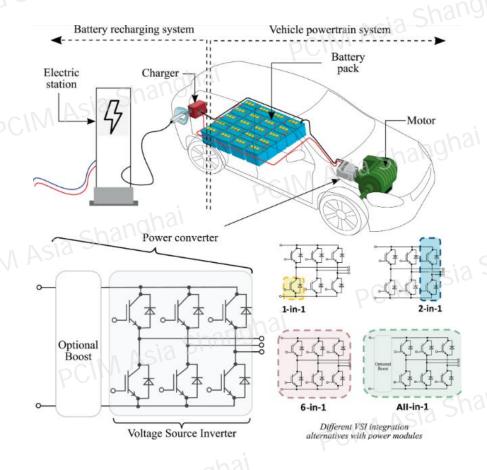

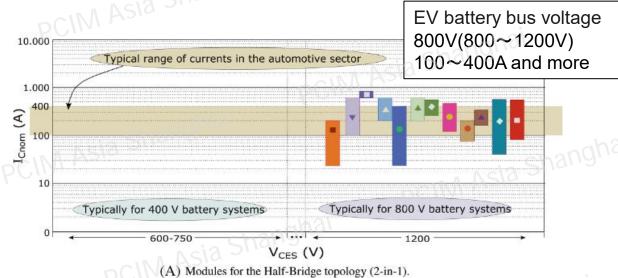

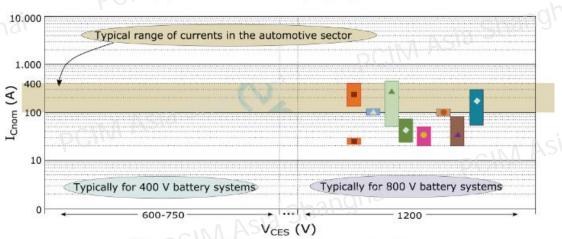

#### **EV** traction inverters

Source:

https://onlinelibrary.wiley.com/doi/full/10.1002/er.8581

The role of power device technology in the electric vehicle powertrain

(B) Modules for the Voltage Source Inverter topology (6-in-1).

Source: https://onlinelibrary.wiley.com/doi/full/10.1002/er.8581 The role of power device technology in the electric vehicle powertrain

#### **Power Module Packaging Technologies**

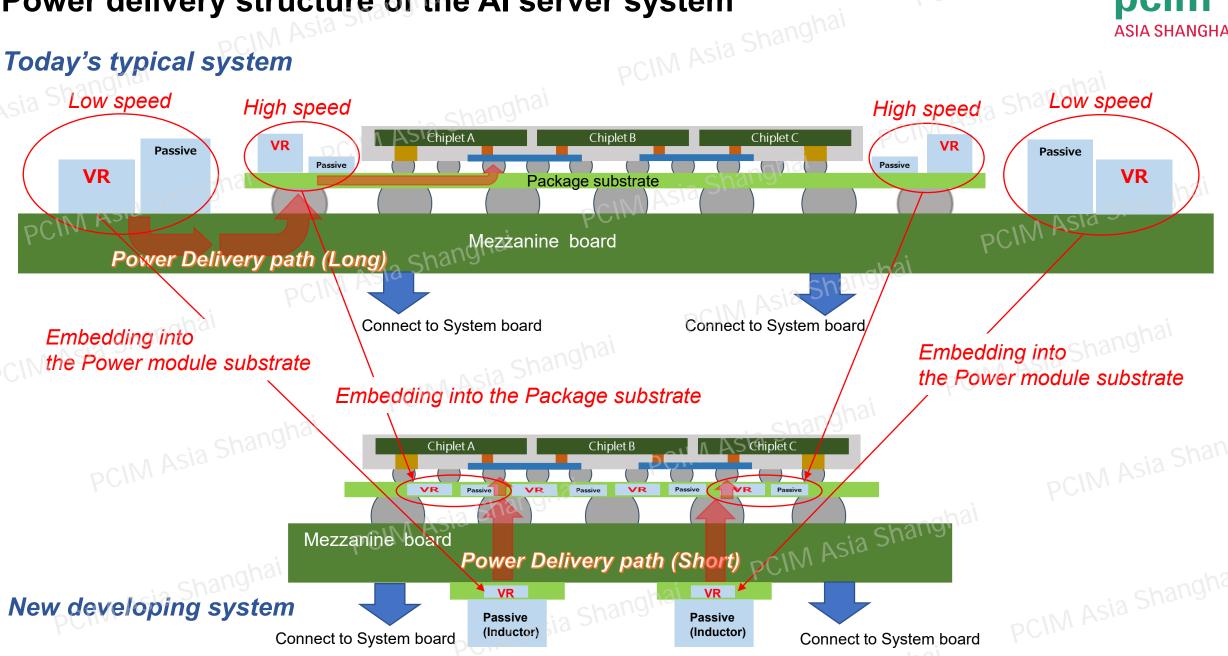

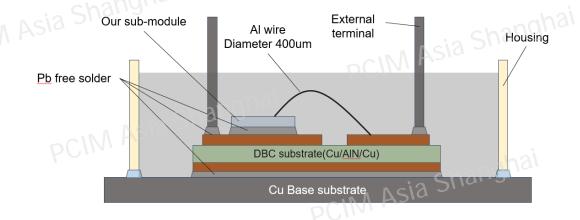

Several SiC inverter modules (packages) have been proposed, but further concept development is needed in terms of heat dissipation, high current, parasitic resistance, inductance and scalability.

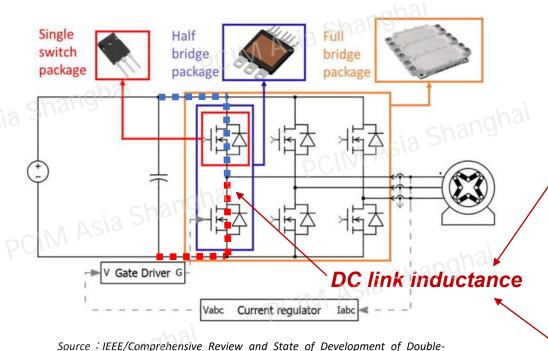

#### Current module (package) trends

Sided Cooled Package Technology for Automotive Power Modules

Larger mounting space

Discrete type

Need many packages (Cost)

· High parasitic inductance

- High customizable package design

- Complicated wiring

- Thinning down is limited due to wire loops

- · High parasitic inductances due to long wire loops

- Wire bonding junction failure in reliability

#### Parasitic inductance of each module

#### **Power Modules**

Towards Planar Power

Conventional Module

Wire Bonds (Al or Cu)

→ 30 - 100 nH

eMPack® module stray inductance ~2.5 nH ~ 6 nH incl. capacitor ( eMPack® ref. design)

Source: Semikron Danfoss Webinar: eMPack Power Module Family

#### Semikron Danfos - eMPack®

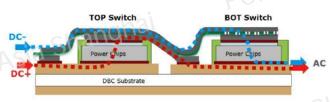

SKiM® technology – flex on top → 2.5 nH Chip Embedded Technology can make the DC loop very short to reduce parasitic inductance (< 1nH)

#### Embedding Module

Flat PCB Cu wiring on top

→ 0.5 nH

Source: NEPCON Japan 2025 Fraunhofer IZM

#### Panel Level chip embedded technology

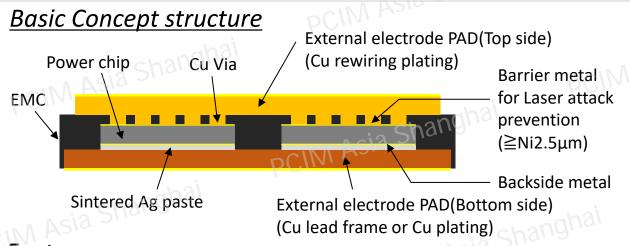

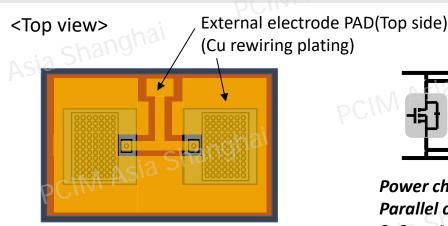

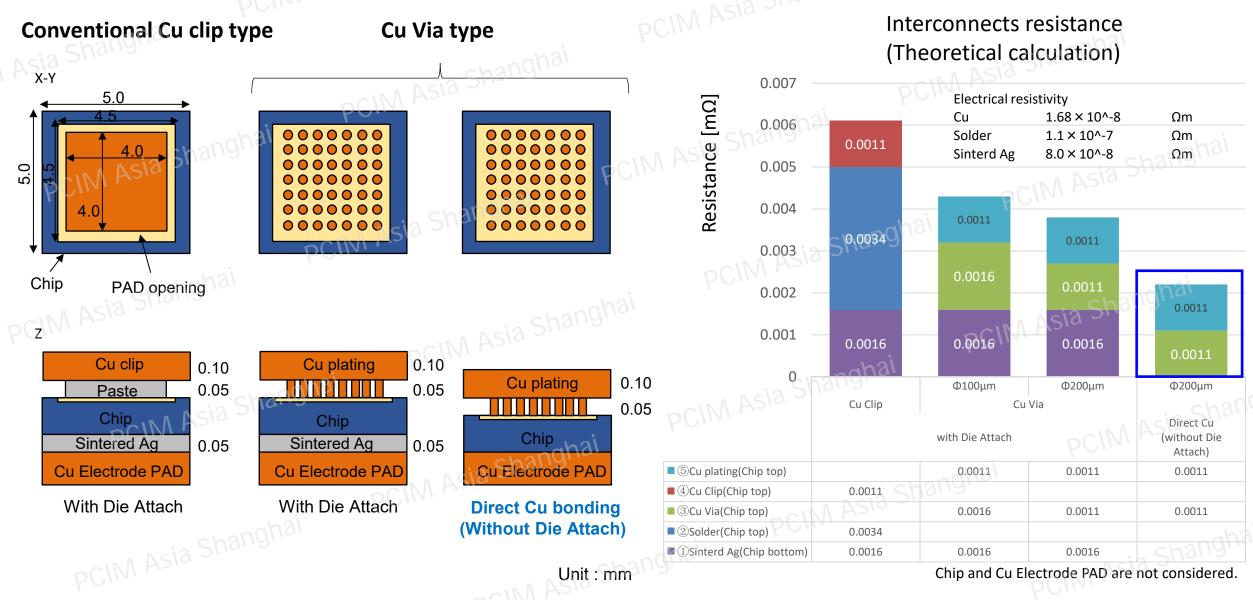

# Proposal for Core Power Module Package using chip-embedded technology with high scalability for inverter applications

Power chip

Parallel connection;

2, 3, ... N parallel

#### *Features*

- Core power module package uses a semi-additive fan-out panel-level process (FOLP \* technology) customized for power applications.

- Cost-effective 300 mm square panel manufacture format.

- Uniquely epoxy coreless substrate and chip embedding technology.

- High current density by power chiplet like (chip parallel connection) technology

- Robust Cu-plated (Via and rewiring) interconnect technology.

- Enhanced High heat dissipation, High current density, low resistance and inductance.

- Integrated in-house production from panel substrate to package assembly.

Actual panel after molding

300 mm square panel format

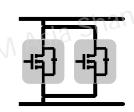

#### **Interconnects Resistance Comparison**

29

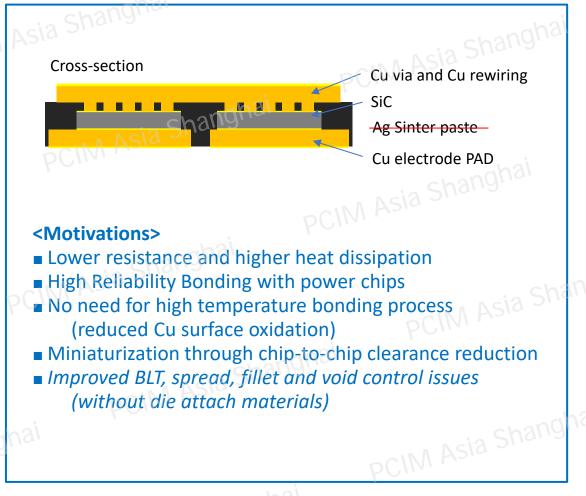

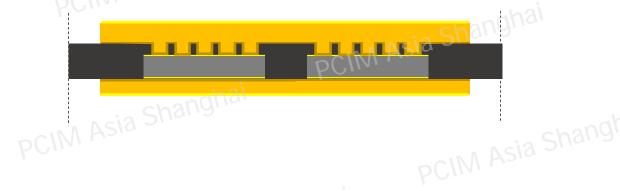

# Panel Level chip embedded Core Power Module (SiC chip Direct Cu plating)

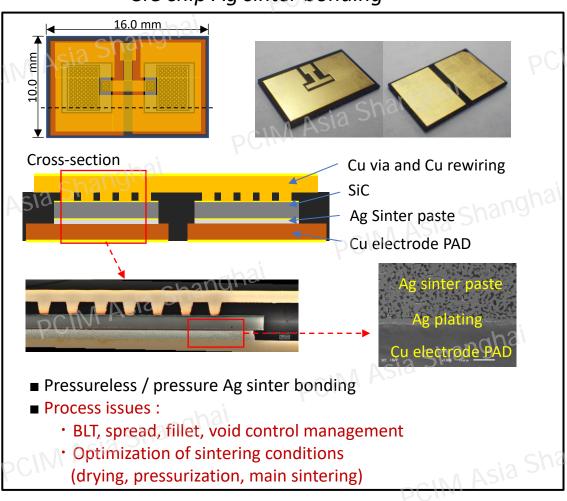

- Technology Innovations in Core Module Packages

- ✓ Basic Technology (IMAPS DPC2024)

SiC chip Ag sinter bonding

✓ New Technology (IMAPS APPE 2024)

SiC chip Direct Cu plating

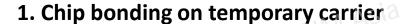

## **Process Flow for Direct Cu Plating** PCIM Asia Shanghai

**Process flow(Tentative)**

3. Temporary Carrier debonding

5. Electrode PAD formation with Cu plating

6. EMC(top side) grinding and Laser via drill on chips

#### **Process flow for Direct Cu plating**

Process flow(Tentative)

9. Via fill and Rewiring with Cu plating

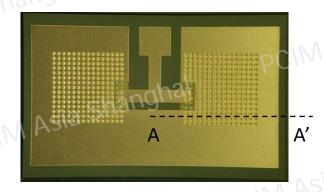

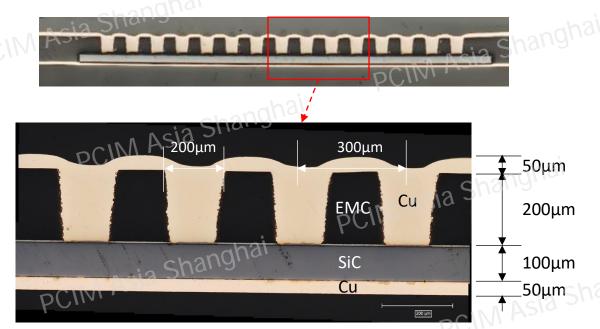

#### **Results of Prototype Sample**

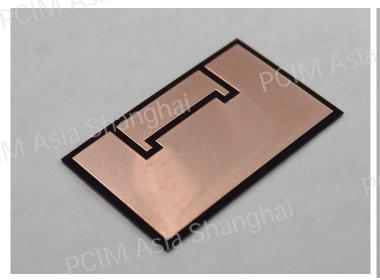

External view of prototype sample

A-A' Cross-section by Microscopic photograph

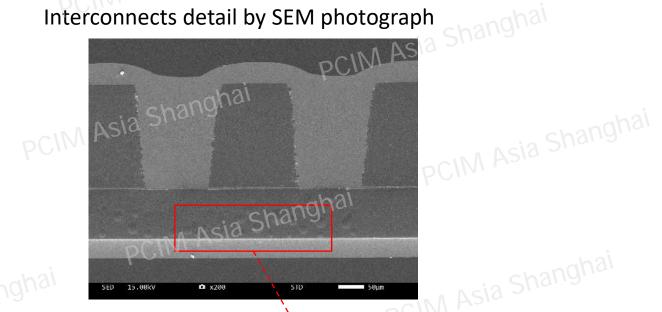

# Interconnects detail by SEM photograph

SiC-Cu Good bonding

# **Prototyping and Reliability Test Results** PCIM Asia Shanghai

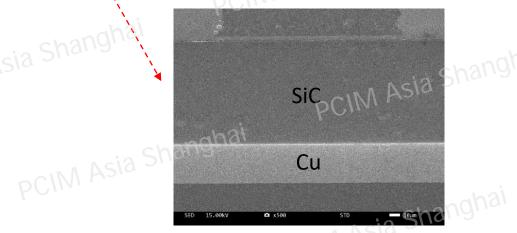

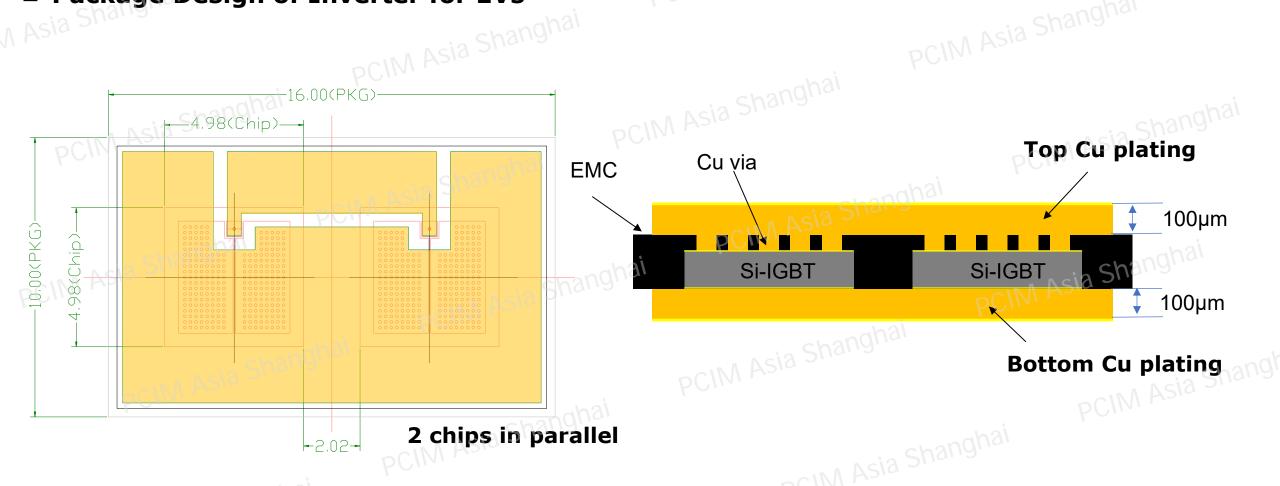

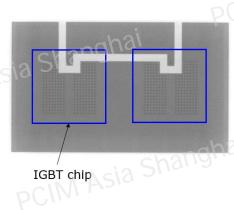

Package Design of Inverter for EVs

# **Prototyping and Reliability Test Results** PCIM Asia Shanghai

#### **■ Finished Prototype**

# Package external image Asia Shanghai

**Bottom**

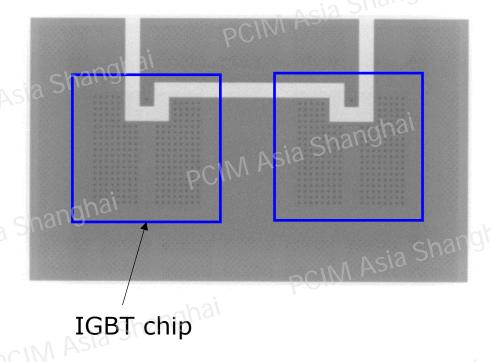

X-ray image

#### CIM Asia Shanghai **Power Cycling Test**

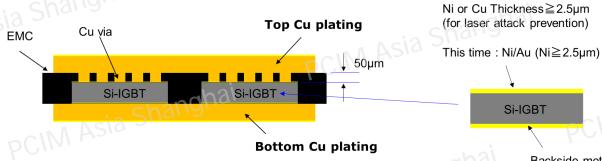

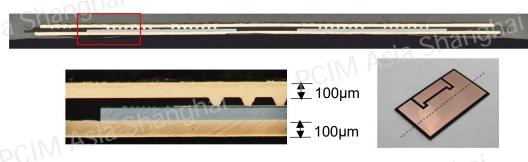

#### √ Package vertical structure and dimensions

Top Cu 100

200

| Cu plating th | nickness(µm) |

|---------------|--------------|

| Cu            | Bottom Cu    |

| 00            | 100          |

200

#### Cross-section image by microscope

#### Level No. A

PCIM Asia Shanghai

#### Level No. B

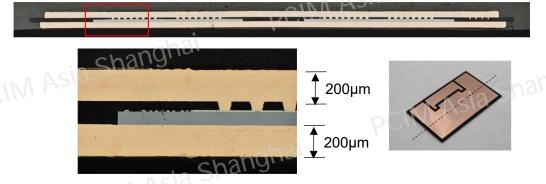

#### Package external image

Level No.

B

#### X-ray image

Barrier metal

Si-IGBT

Backside metal

Ti/Ni/Au

※Trial level

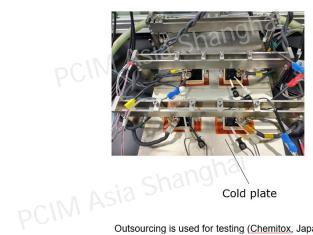

#### **Power Cycling Test Sample structure** PCIM Asia

Cross-section structure

Cold plate

Outsourcing is used for testing (Chemitox, Japan)

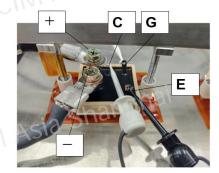

+ : Input current

Output current

C: Collector E: Emitter

G:Gate

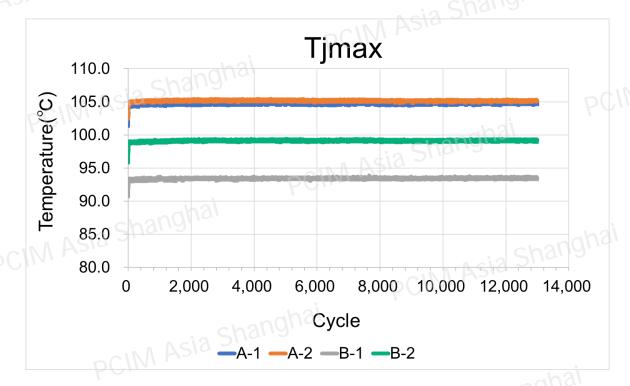

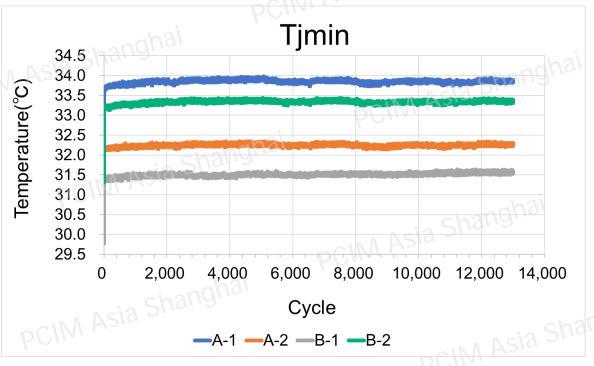

### CIM Asia Shanghai **Power Cycling Test**

#### A Asia Shanghai √ Test conditions

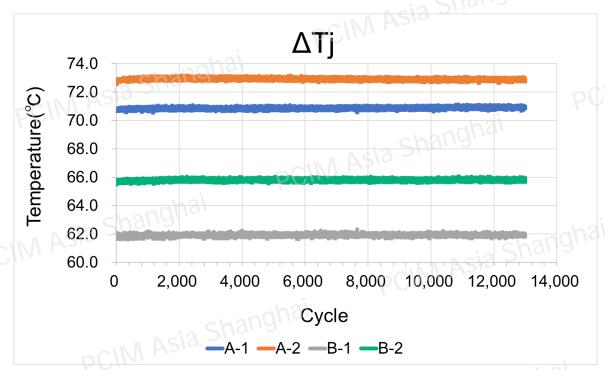

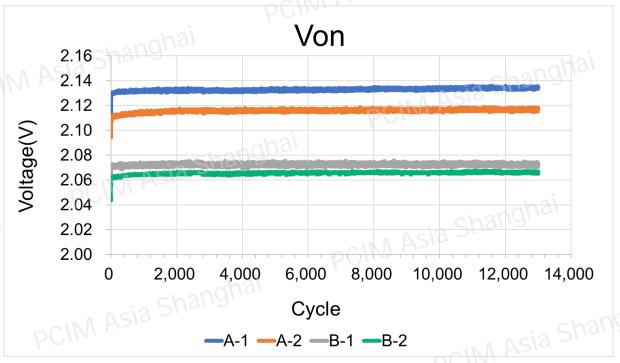

| Ing lest  CIM Asia Shanghar  ✓ Test conditions | PCIM Asia Shanghai                                | AS              |

|------------------------------------------------|---------------------------------------------------|-----------------|

| Items                                          | Conditions                                        | Asia Shanghai   |

| Test mode                                      | Current constant mode : 45A(Between C-E terminal) | Asia Sila.      |

| Cold plate temperature                         | 25°C                                              | _               |

| Number of Si-IGBT chips                        | 1 chip Asia Shang                                 | ch              |

| ΔTj                                            | A sample : 75°C<br>B sample : 65°C                | PCIM Asia Sh    |

| ON/OFF time                                    | ON=10sec<br>OFF=20sec                             |                 |

| Number of cycles                               | 13,000 cyc                                        | PCIM Asia Shang |

| 1 71 -                                         | Asia Shangira                                     | PCIM ASIA       |

#### ✓ Judgment items

| Items            | Remarks(means) PCIM Asia Shanghai    |

|------------------|--------------------------------------|

| Tjmax            | Maximum temperature of chip when ON  |

| Timin PCIM ASI   | Maximum temperature of chip when OFF |

| <b>ATi</b> nghai | Tjmax-Tjmin PCIII                    |

| Von              | On-voltage at current application    |

#### **Power Cycling Test**

#### ✓ Power cycling test results

Sample A:Cu thickness 100µm Sample B:Cu thickness 200µm

No characteristic change after 13,000 cycles

Good results

#### **Power Cycling Test**

#### ✓ Power cycling test results

Sample A:Cu thickness 100µm Sample B:Cu thickness 200µm

No characteristic change after 13,000 cycles

Good results

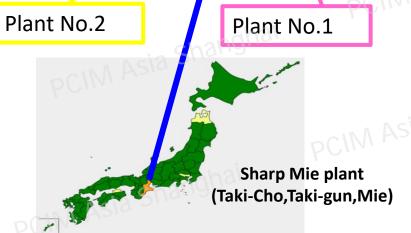

#### New Release: Panel manufacturing capacity expansion

NEWS RELEASE 31 July 2025

#### Regarding the Construction of the Production Line For Advanced Semiconductor Panel Packages at Sharp Mie Plant

By acquiring the second plant in addition to the first plant we already have, we will strengthen our ability to respond to new businesses, including the Advanced Packaging Business, with the aim of quickly launching a production line. At the same time, we will further accelerate the installation of necessary dedicated equipment and strengthening of our human resources structure, aiming to start full-scale operations in fiscal year 2027.

Going forward, by organically linking and optimizing the functions of both factories, we will aim to expand production capacity, streamline processes, and strengthen our supply system, thereby building a flexible and efficient production system that will enable us to respond more quickly to changes in market needs.

#### Summary

- ✓ There is an increasing market requirement for lower resistance and lower inductance, especially in the Al/data center and EV markets.

- ✓ Chip Embedded Technology is attracting a lot of attention due to the above market situation.

- Embedded Technology at the panel level is one of the most promising and realistic candidate.

- ✓ Regarding the AI/Data center market, the key is not only embedding the semiconductor chips but also embedding the passive components for high Power Integrity requirement.

- ✓ Regarding the EV inverter market, the key technologies are interconnection between the chip and metal base, as well as thick Cu RDL wiring. This reduces both electrical and thermal resistance and inductance, thereby improving efficiency.

- ✓ Reliability is the key issue, particularly with regard to interconnection between the chip and the metal, and delamination between each layer (e.g. chip/resin, Cu RDL/resin).